# **General Features**

# **Cryptographic Services**

- Public Key Pair Generation

- Digital Signature

- · Encryption / Decryption

- · Message Digest

- Key Wrapping / Unwrapping

- · Random Number Generation

# **Cryptographic Algorithms**

- DES / 3DES

- AES 128/192/256 bits

- GCM / GMAC

- RSA<sup>®</sup> up to 4096 bits\*

- DSA up to 2048 bits

- ECC up to 576 bits

## **Software Features**

- FIPS 140-2 Identity-based authentication using password, Secure Channel Protocol (SCP02 / SCP03) or Microsoft<sup>®</sup> Smart Card Minidriver strong authentication

- Rights Management (Administrator, Approved User, Non-approved User...)

- Embedded Dynamic FAT12 File System

# **Memory**

- File System 16 Kbytes

- · Write Endurance 500 Kcycles / Data Retention 50 Years

- · 7-Slot ephemeral Key Ring

### Communication

- · USB 2.0 Full Speed Certified, USB CCID compliant

- Slave SPI Serial Interface, WISeKey's Proprietary Protocol

- I<sup>2</sup>C (Two Wire Interface), WISeKey's Proprietary Protocol

# **Packages**

- · QFN20 (RoHS compliant) 4mm x 4mm

- · SOIC8 (RoHS compliant) 5mm x 5mm

### **Hardware Platform**

- 8-/16-bit RISC CPU

- Hardware Random Number Generator

- Hardware 3DES Crypto Accelerator (up to168-bit keys)

- Hardware AES Crypto Accelerator

- · Hardware 32-bit Public Key Crypto Accelerator

### **Certifications / Standards**

- EAL5+

- NIST CAVP

- Microsoft Smart Card Minidriver compliant

- SSL support

- PKCS#11

\*Key sizes supported:

- Linear key size up to 2888 bits for CRT format only (2240 bits otherwise)

- 4096 bits for: CRT only Private exponent, Public exponent, CRT key generation.

- Not available in FIPS mode

#### 1. Overview

The VaultIC405 1.2.1 is a secure microcontroller solution designed to secure various systems against counterfeiting, cloning or identity theft. It is a hardware security module that can be used in many applications such as IP protection, access control or hardware protection.

The proven technology used in VaultIC405 1.2.1 security modules is already widespread and used in national ID/health cards, e-passports, bank cards (storing user Personal Identification Number, account numbers and authentication keys among others), pay-TV access control and cell phone SIM cards (allowing the storage of subscribers' unique ID, PIN code, and authentication to the network), where cloning must definitely be prevented.

Strong Authentication capability, secure storage and flexibility thanks to the various interfaces (USB, SPI, I²C), low pin count and low power consumption are main features of the VaultIC405 1.2.1. Its embedded firmware provides advanced functions such as Identity-based authentication, large Cryptographic command set, various Public domain cryptographic algorithms, Cryptographic protocols, Secure Channel Protocols, Robust communication protocol.

### 1.1 Tamper resistance

WISeKey's security modules will advantageously replace complex and expensive proprietary anti-tampering protection system. Their advantages include low cost, ease of integration, higher security and proven technology.

They are designed to keep contents secure and avoid leaking information during code execution. While on regular microcontrollers, measuring current consumption, radio emissions and other side channels attacks may give precious information on the processed data or allow the manipulation of the data. WISeKey's secure microcontrollers' security features include voltage, frequency and temperature detectors, illegal code execution prevention, tampering monitors and protection against side channel attacks and probing. The chips can detect tampering attempts and erase sensitive data on such events, thus avoiding data confidentiality being compromised.

These features make cryptographic computations secure in comparison with regular microcontrollers whose memories can be easily duplicated. It is much safer to delegate cryptographic operations and storage of secret data (keys, identifiers, etc.) to an WISeKey microcontroller.

### 1.2 Authentication capability

The methods to authenticate humans are generally classified into three cases: physical attribute (e.g. fingerprint, retinal pattern, facial scan, etc.), security device (e.g. ID card, security token, software token or cell phone) and something the user knows (e.g. a password/passphrase or a personal identification number).

To fight against identity theft, the multi-factor authentication is a stronger alternative to the classical login/password authentication (called weak authentication). It combines two or more authentication methods (often a password combined with a security token). Two-factor systems greatly reduce the likelihood of fraud by requiring the presence of a physical device used together with a password. If the physical device is lost or the password is compromised, security is still intact. NIST's authentication guideline [R2] can be referred to for further details.

Multi-factor authentication requires a strong authentication. Anticloning is safely implemented through one-way or mutual strong authentication. Various authentication protocols exist (as specified in ISO9798-2 [R3] or FIPS196 [R4]), but the main method is the **challenge response authentication**:

- 1. The authenticator sends a challenge (e.g. a random number) to the equipment that must be authenticated ("the claimant").

- 2. The claimant computes a digital signature of the combination of this challenge with an optional identifier, using a private or secret key. The requested signature is then returned to the authenticator.

- The authenticator checks the signature using either the same secret key or the public key associated to the claimant's private key and decides whether the claimant is authorized or not based on the signature verification result.

This strong authentication method requires storing secret data. Pure software multi-factor solutions are thus not reliable.

### 1.3 Secure storage

If sensitive data is stored in files on a hard disk, even if those files are encrypted, the files can be stolen, cloned and subjected to various kinds of attacks (e.g. brute force or dictionary attack on passwords). Therefore secure microcontrollers-based hardware tokens are a must. Placing secrets outside the computer avoids risking exposure to malicious software, security breaches in web browsers, files stealing, etc.

# 1.4 Flexibility

The VaultIC405 1.2.1 product features:

- Various communication interfaces including SPI (Serial Protocol Interface), I<sup>2</sup>C (Two Wire Interface) or USB (Universal Serial Bus).

- Low pin count (Vcc, GND, and communication interface specific pins) making integration into an existing board simple. VaultIC405 1.2.1 modules are available in small packages (SOIC8 or QFN20) to fit into the most size-constrained devices.

- Low power consumption, in order to extend battery life in portable devices and low-power systems. VaultIC405 1.2.1 devices consume less than 300µA in standby mode, and only 10 to 20mA during CPU-intensive operations depending on the required action.

- Embedded firmware that provides advanced functions:

- Secure storage: a fully user-defined non-volatile storage of 16KBytes for sensitive or secret data.

- Identity-based authentication with user, administrator and manufacturer roles supported.

- Cryptographic command set to perform cryptographic operations using keys and data from the file system including: authentication, digital signature, encryption/decryption, hash, one-time password generation, random generation and public key pair generation.

- Public domain cryptographic algorithms such as DES, 3DES, AES, RSA PKCS#1 v2.1, DSA, EC-DSA, MAC using DES, 3DES or AES

- Cryptographic protocols such as secret-key unilateral or mutual authentication [R3] and public key based unilateral or mutual authentication [R4].

- Secure Channel Protocol using 3DES or AES.

- Robust communication protocol stacked over the physical communication interfaces.

- Starter Kit with RSA PKCS#11 [R5] and Microsoft MS-CAPI [R6] libraries.

WISeKey's application note [R7] presents examples of efficient and cost effective IP protection applications utilizing secure chips in various embedded systems.

### 1.5 Typical application

The VaultIC405 1.2.1 is a turnkey solution that combines powerful cryptographic capabilities and secure data storage. A typical application of the VaultIC405 1.2.1 is the USB authentication tokens.

These tokens are carried by the employees and are mainly used for user authentication, private key and certificate storage (unlock workstations, gain access to network resources, sign and encrypt emails etc). Authentication tokens based on secure microcontrollers allow to implement high-security IT standards (EAL 5+, ISO27001, ...). Public Key Infrastructures can be trusted since private keys and certificates are only handled by secure microcontrollers and can never be extracted. Convenient biometric authentication can also be implemented without privacy concerns, because fingerprint templates are handled and processed by secure controllers and are not subject to spying. Should a token be lost, it would be no issue since only the holder of the token knows the PIN code or has the right biometric attribute. No sensitive data is ever outside in the clear.

Below is described an example of a VaultlC405 1.2.1 product as USB Token.

Figure 1-1. USB Token Application

For more details about this solution, please refer to the Application Note "How to secure USB e-Token using VaultIC Security Modules?" [R7].

### 1.6 Ordering Information

## 1.6.1 Legal

A Non-Disclosure Agreement must be signed with WISeKey.

An **Export License** for cryptographic hardware/software must be granted.

#### 1.6.2 Quotation and Volume

For minimum order quantity and the annual volume, please contact your local WISeKey sales office.

#### 1.6.3 Part Number

| Reference              |                     | Description                                                                                              |

|------------------------|---------------------|----------------------------------------------------------------------------------------------------------|

|                        |                     | xxx : Chip "Chrono" Number*                                                                              |

| ATVAULTIC405-xxx-P     |                     | P = Z : QFN20 Package                                                                                    |

|                        |                     | R : SOIC8 Package                                                                                        |

| Reference              | <b>A</b> pplication | Description                                                                                              |

| ATVAULTIC-STK01-405R-x | USB Token           | Starter Kit for VaultIC405 1.2.1 in SOIC8 package - USB configuration + USB Dongles                      |

| ATVAULTIC-STK01-405Z-x | USB Token           | Starter Kit for VaultIC405 1.2.1 in QFN20 package - USB configuration + USB Dongles                      |

| ATVAULTIC-STK02-405R-x | Embedded Security   | Starter Kit for VaultIC405 1.2.1 in SOIC8 package - SPI/I²C configuration                                |

| ATVAULTIC-STK02-405Z-x | Embedded Security   | Starter Kit for VaultIC405 1.2.1 in QFN20 package - SPI/I²C configuration                                |

| ATVAULTIC-STK12-405R-x | Embedded Security   | Starter Kit for VaultIC405 1.2.1 in SOIC8 package - SPI/I²C configuration (SPI/I²C adapter not included) |

| ATVAULTIC-STK12-405Z-x | Embedded Security   | Starter Kit for VaultIC405 1.2.1 in QFN20 package - SPI/I²C configuration (SPI/I²C adapter not included) |

<sup>\*</sup> For more details about the Chip "Chrono" Number, please contact your local WISeKey sales office.

#### 1.6.4 Starter Kit

The VaultIC405 1.2.1 Starter Kit provides an easy path to master the cryptographic and secure data storage features of the VaultIC405 1.2.1 secure modules. The content is :

- VaultIC405 1.2.1 samples with 1 dedicated test socket

- VaultIC405 1.2.1 USB dongles or 1 generic USB to SPI / I<sup>2</sup>C adapter (optional)

- 1 CD-ROM containing a support documentation set (getting started, application notes, reference design), some demo applications to get an insight into the VaultIC4xx features, the "VaultIC Manager" tool to design the file system and to personalize samples, a hardware independent cryptographic API with source code, libraries such as PKCS#11 and Microsoft CSP mini-driver.

Figure 1-2. Starter Kit VaultIC405 1.2.1 - Example of content

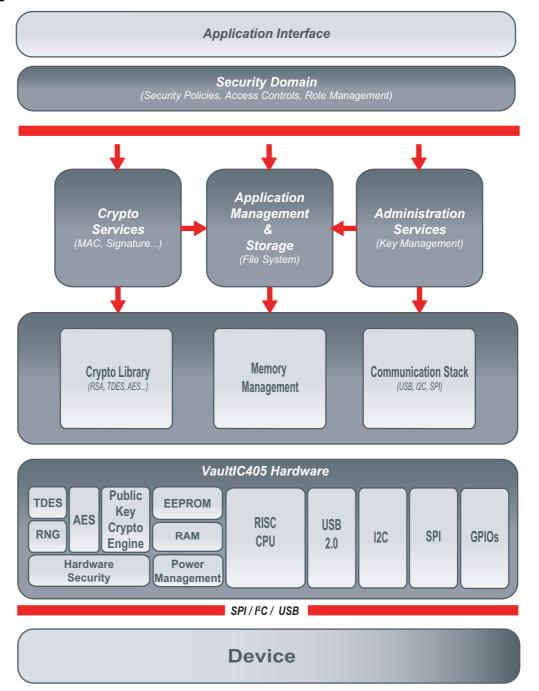

### 1.7 Software and Hardware Architecture

The VaultIC405 1.2.1 software architecture is as shown on the diagram below.

Figure 1-3. Software and Hardware Architecture

# 2. Detailed Features

### 2.1 Communication Interfaces

The VaultIC4xx embeds the following communication interfaces:

• USB 2.0 device full speed (up to 12 Mbps)

SPI: up to 8 MbpsI²C: up to 400 kbps

• GPIOs

# 2.2 Security Mechanisms

The table below summarizes the cryptographic algorithms supported by the VaultlC405 1.2.1.

Please refer to the document *VaultIC Generic Datasheet* (TPR0395X- Available under Non-Disclosure Agreement only) for more details.

Table 2-1. Supported Algorithms table

| Cryptographic Services  | Supported Algorithms                                                                    |

|-------------------------|-----------------------------------------------------------------------------------------|

|                         | Password authentication                                                                 |

| Strong Authentication   | Generic challenge-response authentication protocolusing digital signatures              |

|                         | • ISO/IEC 9798-2                                                                        |

|                         | • FIPS 196                                                                              |

|                         | Microsoft Smartcard Minidriver                                                          |

|                         | <ul> <li>Global Platform v2.2 SCP02 using 3DES</li> </ul>                               |

|                         | Global Platform v2.2 SCP03 using AES                                                    |

| Public Key-Pair         | PKCS#1.5 RSA keypair generator                                                          |

| Generation              | <ul> <li>ANSI X9.62 DSA keypair generator</li> </ul>                                    |

|                         | ANSI X9.62 ECDSA keypair generator                                                      |

|                         | ISO/IEC 9797-1 MAC algorithm 1 using 3DES<br>with 56-bit keys                           |

| MAC                     | <ul> <li>ISO/IEC 9797-1 CBC-MAC algorithm 3 using<br/>DES with 112-bit keys</li> </ul>  |

| (Message Authentication | • NIST SP 800-38B AES CMAC                                                              |

| Codes)                  | <ul> <li>FIPS 198 HMAC with SHA-1, SHA-224, SHA-<br/>256, SHA-384 or SHA-512</li> </ul> |

|                         | NIST SP 800-38D GMAC                                                                    |

|                         | • PKCS#1 v2.1 RSASSA PSS                                                                |

| Magazaga Signatura      | PKCS#1 v2.1 RSASSA-PKCS1-v1_5                                                           |

|                         | Raw RSA X.509 with no padding                                                           |

| Message Signature       | • FIPS 186-3 DSA                                                                        |

|                         | ANSI X9.62 ECDSA over GFp and GF2m                                                      |

|                         |                                                                                         |

8|24

| Cryptographic Services                   | Supported Algorithms                                                                                                                                                                                                                                                    |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | Data encryption / decryption:                                                                                                                                                                                                                                           |

|                                          | <ul> <li>DES, 2DES-EDE, 3DES-EDE and 3DES-EEE withECB, CBC, CFB or OFB chaining modes</li> <li>AES</li> <li>PKCS#1 v2.1 RSAES-OAEP</li> <li>PKCS#1 v2.1 RSAES-PKCS1-v1.5</li> <li>Raw RSA X509 with no padding</li> <li>NIST SP800-38D GCM</li> </ul>                   |

|                                          | Block chaining modes:                                                                                                                                                                                                                                                   |

| Message <mark>E</mark> ncryption         | • ECB • CBC • OFB • CFB • CTR                                                                                                                                                                                                                                           |

|                                          |                                                                                                                                                                                                                                                                         |

|                                          | Padding methods:                                                                                                                                                                                                                                                        |

|                                          | No padding                                                                                                                                                                                                                                                              |

|                                          | Method 1                                                                                                                                                                                                                                                                |

|                                          | Method 2                                                                                                                                                                                                                                                                |

|                                          | • PKCS 5                                                                                                                                                                                                                                                                |

|                                          | • PKCS 7                                                                                                                                                                                                                                                                |

| HOTP - One-Time Pass-<br>word Generation | OATH Has-based OTP algorithm (RFC 4226)                                                                                                                                                                                                                                 |

|                                          | • SHA-1                                                                                                                                                                                                                                                                 |

|                                          | • SHA-224                                                                                                                                                                                                                                                               |

| Message Digest                           | • SHA-256                                                                                                                                                                                                                                                               |

|                                          | • SHA-384                                                                                                                                                                                                                                                               |

|                                          | • SHA-512                                                                                                                                                                                                                                                               |

| Random Number                            | NIST SP 800-90 Deterministic Random Bit                                                                                                                                                                                                                                 |

| Generation                               | Generator using AES-256 algorithm                                                                                                                                                                                                                                       |

| Key Transport Scheme                     | <ul> <li>NIST SP800-56B Key Transport Scheme based on RSAES-OAEP without key confirmation</li> <li>Generic Key Transport Scheme based on AES</li> <li>Generic Key Transport Scheme based on 3DES-EEE</li> <li>Generic Key Transport Scheme based on 3DES-EDE</li> </ul> |

| Cryptographia Sarvigas  | Supported Algorithms                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cryptographic Services  | Supported Algorithms                                                                                                                                                                                                                                                                                                                                                                   |

|                         | <ul> <li>ANS X9.63 and FIPS SP800-56A Static Unified Model + BSI-TR-03111 ECDH over GFp</li> <li>ANS X9.63 and FIPS SP800-56A Static Unified Model + BSI-TR-03111 ECDH over GF2m</li> <li>ANS X9.63 and FIPS SP800-56A One-Pass DH Model + BSI-TR-03111 ECDH over GFp</li> <li>ANS X9.63 and FIPS SP800-56A One-Pass DH Model + BSI-TR-03111 ECDH over GF2m</li> </ul>                 |

| Key Agreement Scheme    | <ul> <li>ANS X9.63 and FIPS SP800-56A Static Unified Model + ANS X9.63 Standard DH over GFp</li> <li>ANS X9.63 and FIPS SP800-56A Static Unified Model + ANS X9.63 Standard DH over GF2m</li> <li>ANS X9.63 and FIPS SP800-56A One-Pass DH Model + ANS X9.63 Standard DH over GFp</li> <li>ANS X9.63 and FIPS SP800-56A One-Pass DH Model + ANS X9.63 Standard DH over GF2m</li> </ul> |

|                         | <ul> <li>ANS X9.63 and FIPS SP800-56A Static Unified Model + ANS X9.63 Cofactor DH over GFp</li> <li>ANS X9.63 and FIPS SP800-56A Static Unified Model + ANS X9.63 Cofactor DH over GF2m</li> <li>ANS X9.63 and FIPS SP800-56A One-Pass DH Model + ANS X9.63 Cofactor DH over GFp</li> <li>ANS X9.63 and FIPS SP800-56A One-Pass DH Model + ANS X9.63 Cofactor DH over GF2m</li> </ul> |

| Key Derivation Function | <ul> <li>NIST-SP800-56A Concatenation KDF</li> <li>ANS X9.63 KDF</li> <li>Microsoft Smartcard Minidriver Hash KDF</li> </ul>                                                                                                                                                                                                                                                           |

| Cryptographic Services                                  | Supported Algorithms                                                                                             |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                         | Domain Parameters should be internally obtained                                                                  |

|                                                         | <ul> <li>Domain Parameters validated by Trusted Third<br/>Party</li> </ul>                                       |

| A source of Mother of Sour                              | <ul> <li>Domain Parameters validated by Trusted Third<br/>Party according to FIPS 186-4</li> </ul>               |

| Assurance Method for<br>Domain Parameters<br>Validation | <ul> <li>Domain Parameters selected from a set of DP<br/>trusted by Trusted Third Party</li> </ul>               |

| validation                                              | <ul> <li>Domain Parameters validation performed by a<br/>Trusted Third Party but faulty</li> </ul>               |

|                                                         | <ul> <li>Domain Parameters generated by a Trusted<br/>Third Party according to FIPS 186-4 but faulty</li> </ul>  |

|                                                         | <ul> <li>Domain Parameters selected from a set of DP<br/>trusted by Trusted Third Party but faulty</li> </ul>    |

|                                                         | Public Key should be internally obtained                                                                         |

|                                                         | Public Key validated by Trusted Third Party                                                                      |

|                                                         | <ul> <li>Public Key generated by Trusted Third Party<br/>using approved methods</li> </ul>                       |

|                                                         | <ul> <li>Public Key generated in cooperation between<br/>Trusted Third Party and the owner</li> </ul>            |

| Assurance Method for                                    | <ul> <li>Public Key generated/regenerated and pairwise<br/>test performed by Trusted Third Party</li> </ul>      |

| Public Key Validation                                   | <ul> <li>Public Key validation performed by a Trusted<br/>Third Party but faulty</li> </ul>                      |

|                                                         | <ul> <li>Public Key generated by a Trusted Third Party using approved methods but faulty</li> </ul>              |

|                                                         | <ul> <li>Public Key generated in cooperation between<br/>Trusted Third Party and the owner but faulty</li> </ul> |

|                                                         | Public Key generated/regenerated and pairwise<br>test performed by Trusted Third Party but faulty                |

|                                                         | Private Key should be internally obtained                                                                        |

| Assurance Method for<br>Private Key Validation          | Private Key generated by Trusted Third Party using approved method                                               |

# 3. Product Characteristics

## 3.1 Maximum Ratings

Table 3-1. Absolute Maximum Ratings

| Symbol                     | Parameter                               | Min.                 | Max.                   | Units  |

|----------------------------|-----------------------------------------|----------------------|------------------------|--------|

| V <sub>CC</sub>            | Supply Voltage                          | -0.3                 | 7.5                    | V      |

| $V_{IN}$                   | Input Voltage                           | V <sub>SS</sub> -0.3 | V <sub>CC</sub> +0.3   | V      |

| T <sub>A</sub>             | Operating Temperature                   | -40                  | +105                   | °C     |

| E <sub>EEPROM</sub>        | EEPROM Endurance for write/erase cycles |                      | 500 000 <sup>(1)</sup> | cycles |

| t <sub>DataRetention</sub> | EEPROM Data Retention                   |                      | 50 <sup>(2)</sup>      | Years  |

| ESD                        | Electrostatic Discharge (HBM)           |                      | 4<br>1.5 (USB pads)    | kV     |

| Lup                        | Latch-up                                |                      | +/- 200                | mA     |

- 1. At a temperature of 25°C.

- 2. Failure rate <1 ppm at a temperature of 25°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 3.2 AC/DC Characteristics (2.7V - 5.5V range; T= -40°C to +105°C)

Table 3-2. AC/DC Characteristics (2.7V - 5.5V range; T= -40°C to +105°C)

| <b>S</b> ymbol        | Parameter                                                     | Condition                         | Min.                | Typ. | Max.                 | Units |

|-----------------------|---------------------------------------------------------------|-----------------------------------|---------------------|------|----------------------|-------|

| V <sub>CC</sub>       | Supply Voltage                                                |                                   | 2.7                 |      | 5.5                  | V     |

| V <sub>IH</sub>       | Input High Voltage - MISO, MOSI, SCK, SPI_SEL, SS, GPIOs      |                                   | 0.7*V <sub>CC</sub> |      | V <sub>CC</sub> +0.3 | V     |

| $V_{IL}$              | Input Low Voltage - MISO, MOSI, SCK, SPI_SEL, SS, GPIOs       |                                   | -0.3                |      | 0.2*V <sub>CC</sub>  | ٧     |

| I <sub>IH</sub>       | Leakage High Current - MISO, MOSI,<br>SCK, SPI_SEL, SS, GPIOs | V <sub>IN</sub> = V <sub>IH</sub> | -10                 |      | 10                   | μΑ    |

| I <sub>IL</sub>       | Leakage Low Current - MISO, MOSI,<br>SCK, SPI_SEL, SS, GPIOs  | V <sub>IN</sub> = V <sub>IH</sub> | -40                 |      | 10                   | μΑ    |

| V <sub>OL</sub>       | Output Low Voltage - MISO, MOSI,SCK, SS, GPIOs                | I <sub>OL</sub> = 1mA             | 0                   |      | 0.1*V <sub>CC</sub>  | >     |

| V <sub>OH</sub>       | Output High Voltage - SS, MISO, MOSI, SCK, GPIOs              | I <sub>OH</sub> = 1mA             | 0.7*Vcc             |      | Vcc                  | ٧     |

| R <sub>I/O</sub>      | Pin Pull-up SPI_SEL,SS                                        |                                   |                     | 220  |                      | ΚΩ    |

|                       | Supply Current in Law Dower                                   | Vcc=3V                            |                     |      | 230                  | μΑ    |

| I <sub>cc LowPw</sub> | Supply Current in Low Power                                   | Vcc=5V                            |                     |      | 240                  | μΑ    |

| I <sub>cc Run</sub>   | Supply Current in RUN Mode when no crypto running             | CLK=35MHz<br>Vcc=3V or 5V         | 4.6                 | 5.4  | 6                    | mA    |

| Symbol                        | Parameter                                                | Condition                 | Min. | Typ. | Max. | Units |

|-------------------------------|----------------------------------------------------------|---------------------------|------|------|------|-------|

| I <sub>cc</sub><br>Run_Periph | Supply Current in RUN mode during RSA/ECC authentication | CLK=35MHz<br>Vcc=3V or 5V | 15.7 | 18.3 | 20   | mA    |

| I <sub>cc DES</sub>           | Supply Current add-on when DES running                   | CLK=35MHz<br>Vcc=3V or 5V | 1.3  | 1.5  | 1.7  | mA    |

| I <sub>cc AES</sub>           | Supply Current add-on when AES running                   | CLK=35MHz<br>Vcc=3V or 5V | 4.2  | 4.7  | 5.2  | mA    |

**Table 3-3.** AC Characteristics (2.7V - 5.5V range; T= -40°C to +105°C)

| Symbol         | Parameter                          | Condition                                                 | Min. | Typ. | Max. | Units |

|----------------|------------------------------------|-----------------------------------------------------------|------|------|------|-------|

|                | I/O Output Rise Time (HRD<br>Mode) | $C_{out}$ =30pF<br>$R_{pullup}$ =20k $\Omega$<br>3V       | 3.1  | 6    | 9.1  | ns    |

|                |                                    | $C_{out}$ =30pF<br>$R_{pullup}$ =20k $\Omega$<br>5V       | 2.3  | 4    | 5.4  | ns    |

| т              | I/O Output Fall Time               | C <sub>out</sub> =30pF<br>R <sub>pullup</sub> =20kΩ<br>3V | 2.4  | 3.7  | 7.3  | ns    |

| T <sub>f</sub> | I/O Output Fall Time               | $C_{out}$ =30pF<br>$R_{pullup}$ =20k $\Omega$<br>5V       | 2.1  | 3.2  | 5.3  | ns    |

# 3.3 Timings

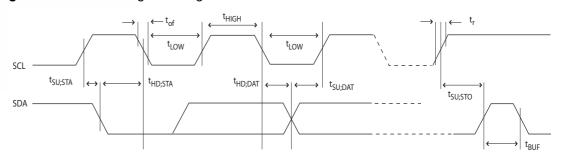

### 3.3.1 I<sup>2</sup>C Timings

The table below describes the requirements for devices connected to the I<sup>2</sup>C Bus. The VaultIC405 1.2.1 I<sup>2</sup>C Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 3-1.

Table 3-4.

I<sup>2</sup>C Timings Parameters

| Symbol              | Parameter                                          | Condition                                             | Min. | Max. | Units |

|---------------------|----------------------------------------------------|-------------------------------------------------------|------|------|-------|

| f <sub>SCL</sub>    | SCL Clock Frequency                                |                                                       |      | 400  | kbps  |

| t <sub>SU;STA</sub> | Set-Up Time for a (repeated) START Condition       |                                                       | 70   |      | ns    |

| t <sub>HD;STA</sub> | Hold Time (repeated) START Condition               | After this period, the first clock pulse is generated | 70   |      | ns    |

| t <sub>LOW</sub>    | Low Period of the SCL Clock                        |                                                       | 490  |      | ns    |

| t <sub>HIGH</sub>   | High period of the SCL clock                       |                                                       | 130  |      | ns    |

| t <sub>HD;DAT</sub> | Data hold time                                     |                                                       | 40   |      | ns    |

| t <sub>SU;DAT</sub> | Data setup time                                    |                                                       | 50   |      | ns    |

| t <sub>su;sto</sub> | Setup time for STOP condition                      |                                                       | 70   |      | ns    |

| t <sub>BUF</sub>    | Bus free time between a STOP and a START condition |                                                       | 1.3  |      | μs    |

Figure 3-1. I<sup>2</sup>C Timings chronograms

Parameters  $t_{\text{of}}$  and  $t_{\text{r}}$  depend on the Host.

These timings refer to Hardware communication parameters. For protocol timings, please refer to *VaultlC405 Product Release Note* (ref TPR0554X).

## 3.3.2 SPI Timings

The table below describes the requirements for devices connected to the SPI. The VaultIC405 1.2.1 SPI meets or exceeds these requirements under the noted conditions.

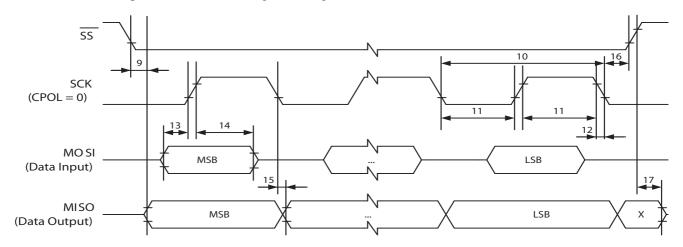

Timing symbols refer to Figure 3-2.

Table 3-5. SPI Timing Parameters

| Symbol | Parameter                                                  | Condition                                        | Min. | Typ. | Max. | Units |

|--------|------------------------------------------------------------|--------------------------------------------------|------|------|------|-------|

| SCK    | Slave Frequency supported                                  | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF |      |      | 8    | MHz   |

| 15     | SCK falling to MISO Delay (t <sub>SCKfalling</sub> )       | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF |      |      | 40   | ns    |

| 13     | MOSI Setup time before SCK rises (t <sub>MOSIsetup</sub> ) | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF | 10   |      |      | ns    |

| 14     | MOSI Hold time after SCK rises (t <sub>MOSIhold</sub> )    | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF | 10   |      |      | ns    |

| 9      | SS asserted to MISO time (t <sub>SSMISO</sub> )            | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF |      |      | 6    | μs    |

| 10     | SCK period (t <sub>SCK</sub> )                             | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF | 10   |      |      | ns    |

| 12     | SCK Rise / Fall time (t <sub>r/f</sub> )                   | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF | 10   |      |      | ns    |

| <b>S</b> ymbol | Parameter                                     | Condition                                        | Min. | Typ. | Max. | Units |

|----------------|-----------------------------------------------|--------------------------------------------------|------|------|------|-------|

| 11             | SCK High / Low Period (t <sub>highSCK</sub> ) | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF | 15   |      |      | ns    |

| 16             | SCK Falling to SS Rising                      | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF | 10   |      |      | ns    |

| 17             | SS high to tri-state                          | C <sub>OUT</sub> =10pF<br>C <sub>OUT</sub> =20pF | 10   |      |      | ns    |

Figure 3-2. SPI Timings chronograms

These timings refer to Hardware communication parameters. For protocol timings, please refer to *VaultlC405 Product Release Note* (ref TPR0554X).

# 3.4 Connections for Typical Application

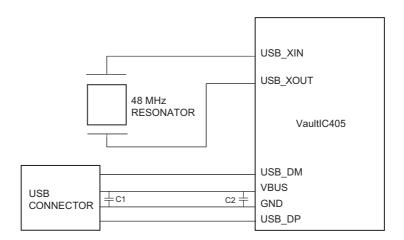

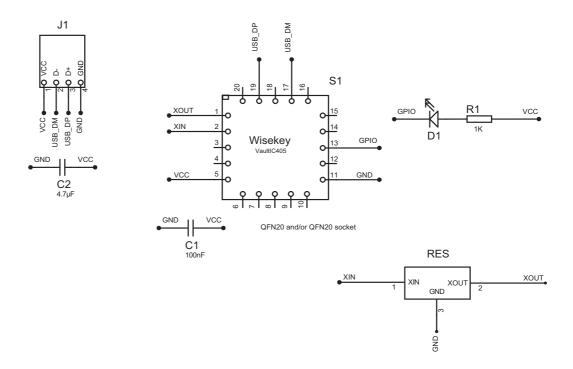

Figure 3-3. VaultIC405 1.2.1 connections for USB typical application

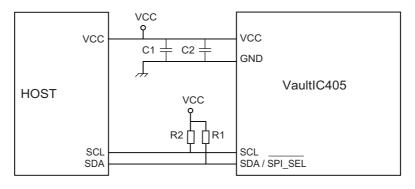

Figure 3-4. VaultIC405 1.2.1 connections for I<sup>2</sup>C typical application

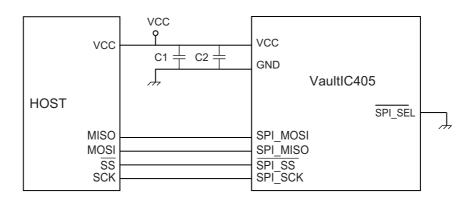

Figure 3-5. VaultIC405 1.2.1 connections for SPI typical application

**Table 3-6.** External components, Bill of Materials

| Configuration    | Reference | Description                        | Typ.Value | Comment     |

|------------------|-----------|------------------------------------|-----------|-------------|

|                  |           | Ceramic Resonator                  | 48MHz     | Mandatory   |

| USB              | C1        | Power Supply Decoupling Capacitors | 4.7 µF    | Recommended |

|                  | C2        | Power Supply Decoupling Capacitors | 10 nF     | Recommended |

|                  | R1, R2    | Pull-Up Resistors                  | 2.2 kΩ    | Recommended |

| l <sup>2</sup> C | C1        | Power Supply Decoupling Capacitors | 4.7 µF    | Recommended |

|                  | C2        | Power Supply Decoupling Capacitors | 10 nF     | Recommended |

| SPI              | C1        | Power Supply Decoupling Capacitors | 4.7 µF    | Recommended |

|                  | C2        | Power Supply Decoupling Capacitors | 10 nF     | Recommended |

#### 3.4.1 Internal Oscillator characteristics

The internal oscillator is optimized for a 48Mhz ceramic resonator.

**Table 3-7.** Internal oscillator characteristics (T= -25°C to +70°C)

| Code      | Parameter                   | Condition                     | Min. | Typ. | Max. | Unit |

|-----------|-----------------------------|-------------------------------|------|------|------|------|

| Vdd       | Supply voltage              |                               | 1.4  | 1.8  | 2.0  | V    |

| ∆Vdd      | Supply ripple               | rms value, 10kHz to 10Mhz     |      |      | 30   | mV   |

| ldd on    | Current consumption         | External capacitors: 12pF     |      | 4.8  | 7.1  | mA   |

| Freq      | Operating frequency         |                               | 40   |      | 48   | MHz  |

| Duty      | Duty cycle                  |                               | 40   |      | 60   | %    |

| Ton       | Startup time                |                               |      |      | 1    | ms   |

| Pon       | Drive level                 |                               |      |      | 500  | μW   |

| ESR       | Equivalent Serie Resistance | @ 48Mhz                       |      |      | 70   | Ω    |

| Cm        | Motional capacitance        | @ 48MHz                       | 10   |      | 200  | fF   |

| Cshunt    | Shunt capacitance           |                               |      |      | 6.2  | pF   |

| Cload     | Load capacitance            | Max external capacitors: 12pF | 2    |      | 6    | pF   |

| ldd stdby | Standby current consumption |                               |      |      | 1    | μΑ   |

The resonator must be placed as close as possible to the VaultlC405 1.2.1 chip.

The oscillator terminals shall not be used to drive other circuits.

In order to have the right resonator load capacitance, external capacitors must be connected on XIN and XOUT pins. For a given resonator, manufacturer specify a load capacitor value to add in parallel with the component. For a set of 2 caps connected between each oscillator terminal and ground, each of them should be equal to twice the specified load capacitance.

WIS@key

Figure 3-6. External load capacitor

WISeKey recommends to use the ceramic resonator CERALOCK® from *Murata* with the part number *CSTCW48M0X11Mxx-R0*. This ceramic resonator hosts built-in capacitance in a small monolithic chip type. Their electrical properties best fit the WISeKey specifications.

WISeKey recommends also CCR048.0MYC7A15T1 from TDK or NX2016HA/SA 48MHz EXS00A from NDK.

### 3.4.2 Building a USB Token

A **USB reference design** is available for the VaultlC405 1.2.1 chip. WISeKey offers a complete software and hardware solution based on a full USB communication stack, an ICCD compliant library and a USB dongle as target.

Figure 3-7. USB Token schematic - Reference design

Table 3-8.

Bill Of Material - Reference design

| Name | Designation                      | Constructor Ref           |  |

|------|----------------------------------|---------------------------|--|

| S1   | Microcontroller in QFN20 package | WISeKey VaultIC405 1.2.1  |  |

|      |                                  | Murata CSTCW48M0X11xx     |  |

| RES  | 48 Mhz ceramic resonator         | (or TDK CCR048.0MYC7A15T1 |  |

|      |                                  | or NX2016HA 48MHz EXS00A) |  |

| J1   | Plug USB Type A                  | Molex 48037-2000          |  |

| C1   | 100 nF capacitance               | -                         |  |

| C2   | 4.7 μF capacitance               | -                         |  |

| R1   | 1K resistor                      | -                         |  |

| D1   | Diode LED                        | KP-3216MGC                |  |

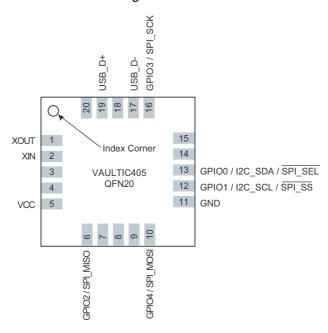

# 3.5 Pin & Package Configuration

## 3.5.1 Pin Configuration

Table 3-9.Pin List Configuration

| Design of the     | Pin #  |           |           |                                                            |  |

|-------------------|--------|-----------|-----------|------------------------------------------------------------|--|

| Designation       | QFN 20 | SOIC8/USB | SOIC8/SPI | Description                                                |  |

| SPI_SCK           | 16     | -         | 5         | SPI clock                                                  |  |

| XOUT              | 1      | 6         | -         | Resonator Signal Input                                     |  |

| XIN               | 2      | 7         | -         | Resonator Signal Output                                    |  |

| vcc               | 5      | 8         | 7         | Power supply                                               |  |

| GPIO0             | 13     | -         | -         | General Purpose IO 0                                       |  |

| SPI_MISO          | 6      | -         | 8         | SPI Master Input Slave Output                              |  |

| SPI_MOSI          | 10     | -         | 1         | SPI Master Output Slave Input                              |  |

| GPIO1             | 12     | -         | -         | General Purpose IO 1                                       |  |

| GND               | 11     | 1         | 2         | Ground (reference voltage)                                 |  |

| GPIO2             | 6      | -         | -         | General Purpose IO 2                                       |  |

| SPI_SS / I2C_SCL  | 12     | 2         | 3         | SPI Slave Select or I <sup>2</sup> C SCL                   |  |

| SPI_SEL / I2C_SDA | 13     | 3         | 4         | SPI/I <sup>2</sup> C selection PIN or I <sup>2</sup> C SDA |  |

| GPIO3             | 16     | -         | -         | General Purpose IO 3                                       |  |

| GPIO4             | 10     | -         | -         | General Purpose IO 4                                       |  |

| USB_DM            | 17     | 4         | -         | USB D- differential data                                   |  |

| USB_DP            | 19     | 5         |           | USB D+ differential data                                   |  |

Other pins are not connected (do not connect to GND).

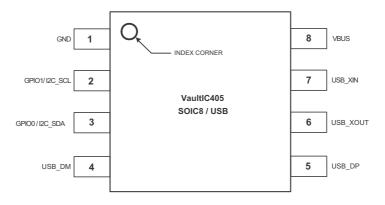

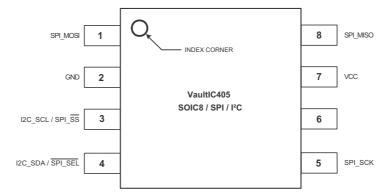

### 3.5.2 Pinouts for packages QFN20 and SOIC8

Figure 3-8. Pinout VaultlC405 1.2.1 - Package QFN20

Note: The exposed pad is connected to GND pin internally. So it is recommended to connect it to GND.

Figure 3-9. Pinout VaultIC405 1.2.1 - Package SOIC8 - USB and I<sup>2</sup>C configurations

Figure 3-10. Pinout VaultIC405 1.2.1 - Package SOIC8 - SPI and I<sup>2</sup>C configurations

### 3.5.3 Packages characteristics

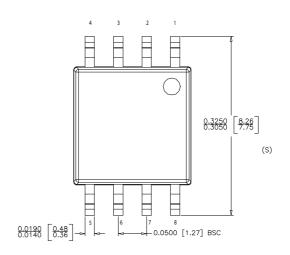

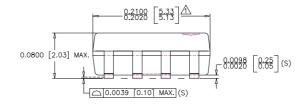

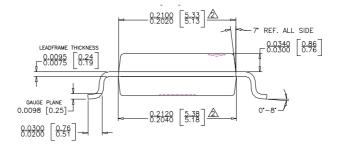

Figure 3-11. SOIC-8 package characteristics

### NOTE:

⚠ DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS AND GATE BURRS SHALL NOT

EXCEED 0.006 INCH PER SIDE.

DOES NOT INCLUDE INTER-LEAD FLASH OR PROTRUSIONS.

INTER-LEAD FLASH AND PROTRUSIONS SHALL NOT

EXCEED 0.010 INCH PER SIDE.

- 3. THIS PART IS COMPLIANT WITH EIAJ SPECIFICATION EDR-7320.

- 4. LEAD SPAN/STAND OFF HEIGHT/COPLANARITY ARE CONSIDERED AS SPECIAL CHARACTERISTIC.(S)

- 5. CONTROLLING DIMENSIONS IN INCHES. [mm]

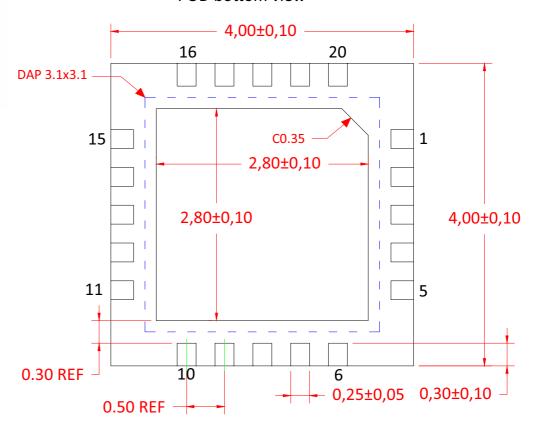

Figure 3-12. QFN-20 package characteristics

### POD bottom view

# POD side view

Dimensions in mm

# 3.6 Product Marking

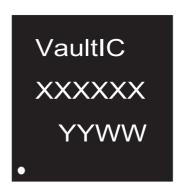

### 3.6.1 QFN20 Package

VaultIC versionning XXXXXX : Lot Number YYWW : Date Code

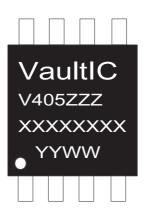

### 3.6.2 SOIC8 Package

VaultIC versionning

ZZZ: Internal Assembly reference

XXXXXXXX : Lot Number YYWW : Date Code

6614GS - 25Sept19

The photographs and information contained in this document are not contractual and may be charged without notice. Brand and product names may be registered trademarks or trademarks of their respective holders.

Note: This is a summary document. A complete document will be available under NDA. For more information, please contact your local WiseKey sales office.