# Features

#### General

- High-performance, Low-power 8/16-Bit RISC Architecture

- 135 Powerful Instructions (Most Executed in a Single Clock Cycle)

- Low Power Idle and Power-down Modes

- Bond Pad Locations Conforming to ISO 7816-2

- ESD Protection to ± 4kV

- Operating Ranges: 2.7 to 5.5V

- Compliant with EMV 4.3 Specifications, PC Industry Compatible

- Available in Wafers, Modules, and Industry-standard Packages

### Memory

- 40K Bytes of Flash Program Memory

- 40K Bytes of EEPROM, Including 128 OTP Bytes and 384 Bit-addressable Bytes

- 1 to 128-byte Program / Erase

- 1ms Program / 1ms Erase

- Typically 500,000 Write/Erase Cycles at a Temperature of 25°C

- 10 Years Data Retention

- EEPROM Erase only mode

- Write EEPROM with or without autoerase

- 8K bytes RAM Memory (6K bytes of CPU RAM, 2K bytes of Ad-X<sup>™</sup> RAM, shared with the CPU core)

## **Development Tools**

- Voyager Emulation Platform (ATV4) to Support Software Development

- IAR Embedded Workbench<sup>®</sup> V5.51 Debugger or Above

- Software Libraries and Application Notes

# Peripheral

- One I/O Port

- One ISO 7816 Controller

- Up to 625 Kbps at 5 MHz

- Compliant with T=0 and T=1 Protocols

- Programmable Internal Oscillator (Up to 36 MHz for Ad-X and 36 MHz for internal CPU Clock)

- Two 16-bit Timers

- Random Number Generator (RNG)

- 2-level Interrupt Controller

- Hardware DES and Triple DES DPA/DEMA Resistant (Four keys)

- Hardware AES

- Code Signature Module

- CRC16 & 32 Engine (Compliant with ISO/IEC 3309)

- 32-Bit Cryptographic Accelerator (Ad-X for Public Key Operations)

- RSA, DSA, ECC, Diffie-Hellman

#### Security

- Dedicated Hardware for Protection Against SPA/DPA/SEMA/DEMA Attacks

- Advanced Protection Against Physical Attack, Including Active Shield, EPO, CStack Checker, Slope Detector, Parity Errors

- Environmental Protection Systems

- Voltage Monitor

- Frequency Monitor

- Temperature Monitor

- Light Protection

- Secure Memory Management/Access Protection (Supervisor Mode)

### **Certification targeted**

• CC EAL5+ (PPSSVG - BSI 0002)

# Description

The AT90SC4040CV is a low-power, high-performance, 8/16-bit microcontroller with Flash program memory and EEPROM memory, based on the RISC architecture.

By executing powerful instructions in a single clock cycle, the AT90SC4040CV achieves throughputs close to 1 MIPS per MHz. Its Harvard architecture includes 32 general- purpose working registers directly connected to the ALU, allowing two independent registers to be accessed in one single instruction executed in one clock cycle.

In addition to the 40K bytes of Flash Program Memory, the AT90SC4040CV includes 40K bytes of high density EEPROM.

The ability to map the EEPROM in the code space allows parts of the program memory to be reprogrammed insystem.

This technology combined with the versatile 8/16-bit CPU on a monolithic chip provides a highly flexible and costeffective solution to many smart card applications.

This product is described in the TPR0323X Application Note (Flash-EEPROM Configuration of AT90SC ROM products). Please contact your local sales office to get the latest version.

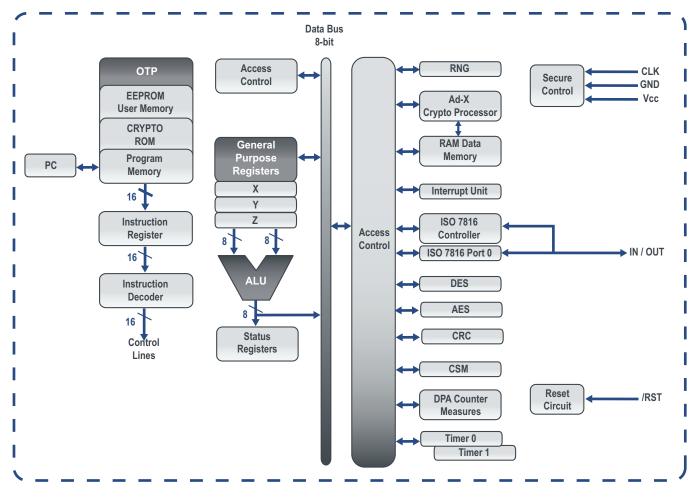

Figure 1 shows a block diagram of the AT90SC4040CV.

#### Figure 1 AT90SC4040CV RISC CPU Core Architecture

The photographs and information contained in this document are not contractual and may be charged without notice. Brand and product names may be registered trademarks or trademarks of their respective holders.

Note: This is a summary document. A complete document will be available under NDA. For more information, please contact your local WiseKey sales office.